Дата публикации:Tue, 24 Oct 2023 17:08:56 +0300

Исследователи из Швейцарской высшей технической школы Цюриха разработали систему fuzzing-тестирования Cascade, нацеленную на выявление ошибок и уязвимостей в процессорах на базе архитектуры RISC-V. Инструментарий уже позволил выявить 37 ошибок в процессорах, из которых 29 были классифицированы как ранее неизвестные уязвимости.

Разработчики Cascade попытались учесть недостатки существующих до этого систем fuzzing-тестирования процессоров, которые ограничивались выполнением лишь коротких порций кода, охватывающих небольшую часть набора инструкций и ограниченное число комбинаций выполнения команд.

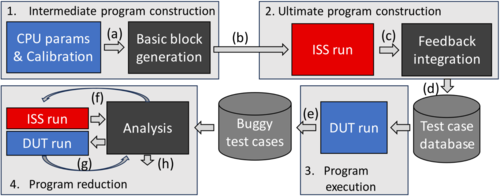

Cascade нацелен на генерацию больших и сложных программ, охватывающих нетривиальные потоки выполнения команд и приводящих к возникновению нетипичных состояний CPU. В Cascade при помощи имеющейся эталонной модели набора инструкций команд RISC-V (RISC-V ISA) формируются изначально корректные большие рандомизированные и связанные между собой потоки выполнения (control flow) и потоки обработки данных (data flow).

Потоки выполнения и данных в сгенерированной программе тесно переплетены, поэтому если в ходе выполнения возникнет ошибка в потоке данных, то она каскадно отразится на дальнейшем ходе выполнения и с большой вероятностью изменит поток выполнения, что приведёт к незавершению программы. Для определения проблемных инструкций в незавершённых программах Cascade постепенно автоматически сокращает выполняемую программу до тех пор, пока не будет найден минимальный набор инструкций, вызывающий ошибку. Подобный подход существенно проще в реализации и быстрее классических методов выявления ошибок, основанных на сверке после каждой выполненной инструкции состояний после фактического выполнения на CPU и после выполнении с использованием эталонной модели.

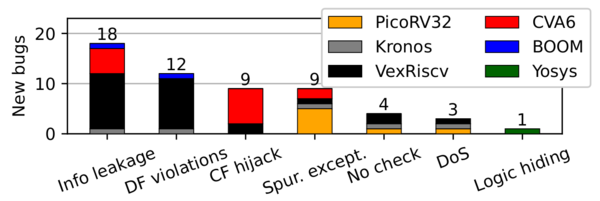

При помощи Cascade были протестированы пять процессоров на базе архитектуры RISC-V - Kronos, PicoRV32, VexRiscv, CVA6 и BOOM, в которых в сумме было выявлено 37 ошибок. Большинство ошибок приводили к проблемам с безопасностью, например, некоторые проблемы вызывали отказ в обслуживании или утечку информации в ходе спекулятивного выполнения инструкций непривилегированным пользователем.

- 12 ошибок приводили к нарушению целостности потока данных, что могло использоваться для изменения результата выполнения определённых вычислений в коде другого пользователя при формировании злоумышленником определённого состояния микроархитектурных структур. Например, ошибка динамического округления в CPU BOOM позволяла атакующему добиться использования в процессе жертвы другого режима округления чисел с плавающей запятой.

18 ошибок приводили к утечке информации, что, например, позволяло атакующему получить доступ по сторонним каналам к состоянию флагов и регистров FPU.

9 ошибок позволяли перехватить поток выполнения, что давало возможность атакующему повлиять на ход выполнения другой программы. Например, ошибка в процессоре CVA6 приводила к выставлению неверных флагов, влияющих на результат вычислений или определение переполнений, а ошибка в процессорах VexRiscv при определённых условиях приводила к неверному выполнению операций сравнения регистров.

9 ошибок связаны с ложной генерацией исключений, что могло использоваться атакующими для обхода режимов изоляции, применяемых в TEE-окружениях (Trusted Execution Environment). Например, к исключению приводило чтение некоторых регистров CSR (Control and Status Register), что позволяло злоумышленнику симулировать взаимодействие с окружением.

4 ошибки вызваны отсутствием должных проверок и позволяли атакующему обойти связанные с безопасностью проверки (например, проверки использования FPU другими ядрами), подставить ложные сведения о доступных возможностях CPU или обмануть программы-анализаторы.

Три ошибки приводили к зависанию процессора при выполнении определённых манипуляций на любом уровне привилегий.

Одна ошибка была классифицирована как возможность встраивания скрытой логики на этапе проектирования чипа (злонамеренный участник мог внести ошибку в проект, передав внешне безобидное описание уровня регистровых передач (RTL)).

Новость позаимствована с opennet.ru

Ссылка на оригинал: https://www.opennet.ru/opennews/art.shtml?num=59986